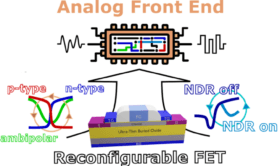

GTS & SENSOTERIC: Exciting Kick-off Meeting in Dresden, Germany

First meeting of the European Union Horizon Project SENSOTERIC about RFET and NDR transistor technologies

Read More

Invited talk at EDTM Bangalore

Our CEO will hold a keynote on “Efficient and Accurate DTCO Framework for Reliability and Variability-Aware Explorations of FinFETs, Nanosheets, and Beyond”, on this year’s EDTM in Bangalore.

Read More

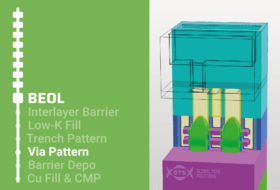

GTS @IEDM2023 – Process to Circuit

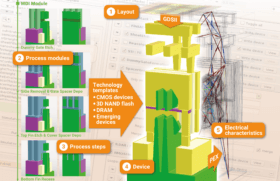

DTCO Flows that Work: Process – physics-based device simulation – circuit simulation. All covered in GTS Framework.

Read More

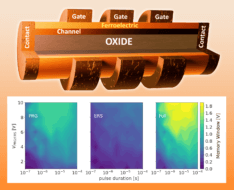

GTS @ ESSDERC 2023: Ferroelectric VNAND Memory

Combine the competing effects of ferroelectricity and charge trapping in a single simulation work-flow in GTS Framework – nicely matching experiment results from literature.

Read More

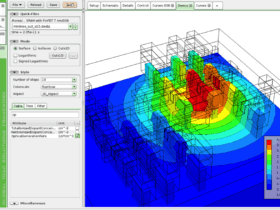

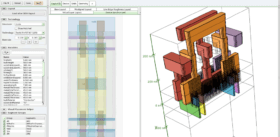

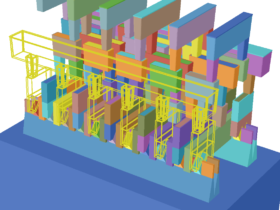

GTS @DAC2023 – DTCO with Process Integration

DTCO, Process, Variability & Yield: Use GTS ProEmu process modules to easily explore designs for new technology platforms. Optimize for device PPA as well as production yield.

Read More

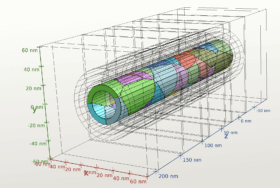

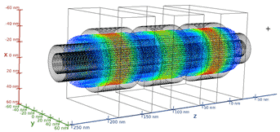

IMW2023: Tutorial on 3D SONOS Flash TCAD Modeling

Franz Schanovsky will share insights about the techniques and challenges of 3D TCAD modeling of a FLASH memory. Join him in Montreal on May 21st, 2023!

Read More

Wanted: Java Developer

We want you for software development for our Java applications, development of distributed systems, some GUI programming and data science and processing!

Read More

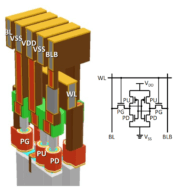

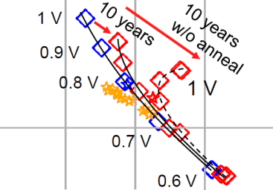

IEDM Paper: Nanosheet SRAM DTCO targeting the 3nm node

In a performance & variability-aware DTCO flow, we benchmark Gate-all-around nanosheets for 3nm. Despite lower parasitic capacitances of fins, nanosheet SRAMs achieve better Vmin, read delay, and footprint.

Read More

ESSDERC 2022 – Paper: Wave-Function Penetration in MOSFETs

GTS presenting novel semi-analytical model for wave-function penetration, resolving long-standing problems such as carrier spillover and large errors in surface roughness scattering.

Read More

GTS @SISPAD2022: CSFET, PCM/PRAM OTS

SISPAD 2022 in Granada: DoS Engineering of Cold-Source FET (CSFET) and Monolithic TCAD Simulation of Phase-Change (PCM/PRAM) + Ovonic Threshold Switch (OTS) Selector Device

Read More

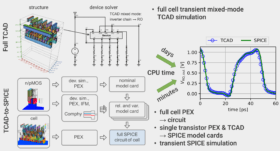

GTS @DAC2022: SPICE up Your TCAD for Fast DTCO

From Days to Minutes: Cut Simulation Time in DTCO, with Full Accuracy. Combining the benefits of TCAD and SPICE, the GTS DTCO flow makes large-cell variability studies a snap.

Read More

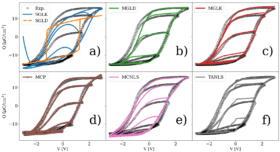

Ferroelectrics: Polycrystalline Thin Films (TED), Hafnia-based gatestacks (IRPS)

In his recent IEEE TED article on ferroelectric polycrystalline thin film modeling, GTS scientist M. Thesberg compares 7 Landau and MC based as well as the Preisach model to experimental data.

Thesberg also contributed to B. Truijen’s paper on trap-polarization interaction during low-field trap characterization on hafnia-based ferroelectric gatestacks.

GTS @IEDM2021 – 3D NAND, AI, DTCO

DTCO Flows that Work: Why physics-based device simulation in fact is a prerequisite for getting dependable and accurate predictions for upcoming technology nodes.

Read More

GTS @DAC2021 – Physical Again, Boosting DTCO

Meet us in real physical space, learn how physics-based device simulation boosts DTCO and path-finding as well as optimizing for reliability and yield.

Read More

SISPAD 2021: Variability-Aware DTCO Flow

On this year’s SISPAD we presented our newest data on Variability-Aware DTCO Flow.

Read More

Virtual ESSDERC 2021: Simulation and Modeling of Defects and Traps

GTS CTO Zlatan Stanojević is chairing session Simulation & Modeling of Defects & Traps together with Denis Rideau (STMicroelectronics) — Thursday September 16, 2021 (16:00-17:00)

Read More

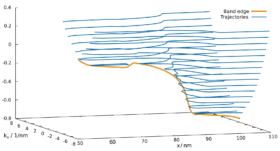

IEEE TED Paper: Nano Device simulator – A Practical Subband-BTE Solver for Path-Finding and DTCO

Initially released in 2015, NDS has evolved to become the standard tool for modeling carrier transport in nano-scale MOSFETs in industry and academia; we disclose details on NDS’ features and methods.

Read More

How can quantum transport models be implemented into device TCAD?

We address this question in one of our research projects, in cooperation with TU Wien: NEDEVS (Nanoelectronic Device Simulation), an FFG national bridge project, which was started at the end of last year and will continue for 2,5 more years.

Read More

NDS and CellDesigner join forces to simulate a radically new SRAM architecture based on SGT

A new SRAM architecture based on vertical surrounding gate transistor (SGT) technology was designed for the 1.5nm node by Unisantis in cooperation with GTS using GTS’ DTCO flow.

Read More

3D NAND Simulation: a new approach for ISPP modeling

New TCAD model solves longstanding discrepancy between predicted and measured incremental step pulse programming (ISPP) data.

Read More

Meet Gerhard Rzepa presenting a Reliability-aware DTCO Flow at Virtual IRPS 2021

This simulation approach, combining TCAD and SPICE, will make future technologies more efficient and reliable.

Read More

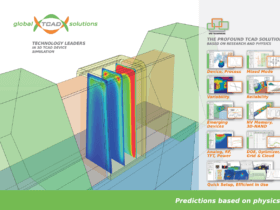

GTS leading the way to process-aware layout-based structure emulation for DTCO

Within our wide range of research projects, we started a new venture in cooperation with TU Wien scientists. The project goal is to establish process-aware layout-based structure emulation for DTCO until end of 2022.

Read More

New GTS Web Site

We have completely revised our web site, for more clarity, improved experience on mobile devices, and a better MyGTS.

Read More

GTS@ Virtual SISPAD 2020: S/D-Tunnelling in 3nm SiGe/Ge

Pioneering for the 3nm node, GTS to present subband BTE solver with fully integrated source/drain-tunneling current calculation based on the WKB-approximation.

Read More

IEEE IEDM: Emerging Transistor Reliability and Pertinent Strategies

GTS Scientist Franz Schanovsky will be co-chairing the session Emerging Transistor Reliability and Pertinent Strategies

Read More

ESSDERC: Chairing session “Multi-physics Modeling”

We are looking forward to seeing you at ESSDERC 2019 in Kraków: Our CTO Zlatan Stanojević will be chairing session C2L-G “Multi-physics Modeling” (Track 3), together with Viktor Sverdlov.

Read More

GTS @SISPAD 2019 in Udine: VNAND SONOS

At the 2019 SISPAD in Udine, we invite you to hear D. Verreck’s talk “3D TCAD Model for Poly-Si Channel Current and Variability in Vertical NAND Flash Memory”, co-autored by GTS scientists.

Read More

Visit us at DAC 2019!

From June 2nd to 6th we will be at the Design Automation Conference 2019 in Las Vegas Convention Center. Download GTS Cell Designer (DAC) flyer, explaining our poster

Read More

GTS is proud to hire the lead developer of compact physics software Comphy

GTS scientific team enhanced by oxide reliability modeling specialist

Read More

New Christian Doppler Lab on “single defect spectroscopy in semiconductor devices”

In the new CD Laboratory at the TU Wien, Infineon Technologies AG, ams AG and Global TCAD Solutions GmbH are working together on understanding the physics of gate oxide reliability in semiconductor devices.

Read More

GTS@IEEE-ICEE in Bangalore – invited talk by Zlatan Stanojević

Zlatan Stanojević, CTO of Global TCAD Solutions, will hold a talk on “Innovation in TCAD from a Start-Up Perspective” in the Modelling and Simulation session, at 15:15 on Dec. 18th, 2018.

Read More

IEDM 2018, MOS-AK Workshop in San Francisco

Visit the GTS booth in the IEDM exhibits area and join our presentation at MOS-AK workshop on Dec 5!

Read More

TCAD in DTCO: Cell Designer – GTS Paper @ ESSDERC 2018

GTS presenting first practical TCAD-based work flow for design-technology co-optimization (DTCO) of standard cells.

Read More

NC-FET, FeRAM: GTS @ VLSI and NCFET Research Grant

Next to its contribution at VLSI/SNW 2018, GTS takes part in a FFG research project to create a 3D TCAD model for ferroelectric materials.

Read More

V-NAND application example: Channel trans-conductance

Mobility reduction at grain boundaries in V-NAND device

Read MoreGTS @ EuroSOI-ULIS 2018: Scaling limits of FD-SOI

Presenting a Physical Modeling Study Based on 3D Phase-Space Subband Boltzmann Transport for Fully-Depleted SOI Technology

Read More

GTS Framework 2018.03

New applications: V-NAND transconductance variability, physical simulation of FD-SOI technology

Read MoreGTS @ IEDM 2017: Cell Simulation, DTCO

Visit the GTS booth in the IEDM exhibits area to learn about our latest products and developments!

Read More

Listed by European Commission Innovation Radar 2017

GTS was identified as one of the top 10 “Best Young SME” by the European Commission Innovation Radar 2017.

Read More

IEEE EDS Delhi Workshop, AICTE / IIT(BHU) Varanasi

GTS workshops at two events in India, coordinated by our partner TNL.

Read More

New GTS Partner in India

TechNextLab becoming GTS partner for distribution and support in India.

Read More

IWRMN-EDHE 2017 Invited Talk: From Impact to Upset

Physical Modeling of Irradiation Effects in nano-scaled CMOS Logic and Memory Devices

Read More

Join our event at VLSI-TSA: DTCO for Advanced Nodes

Towards Physics-based DTCO for N7 and sub-N7 Technologies

Read More

GTS @ 12th ESA Geant4 Space Users Workshop

GTS presenting TCAD modeling toolchain for irradition effects in nano-scale CMOS logic devices using layout-based design

Read More