11. July 2023

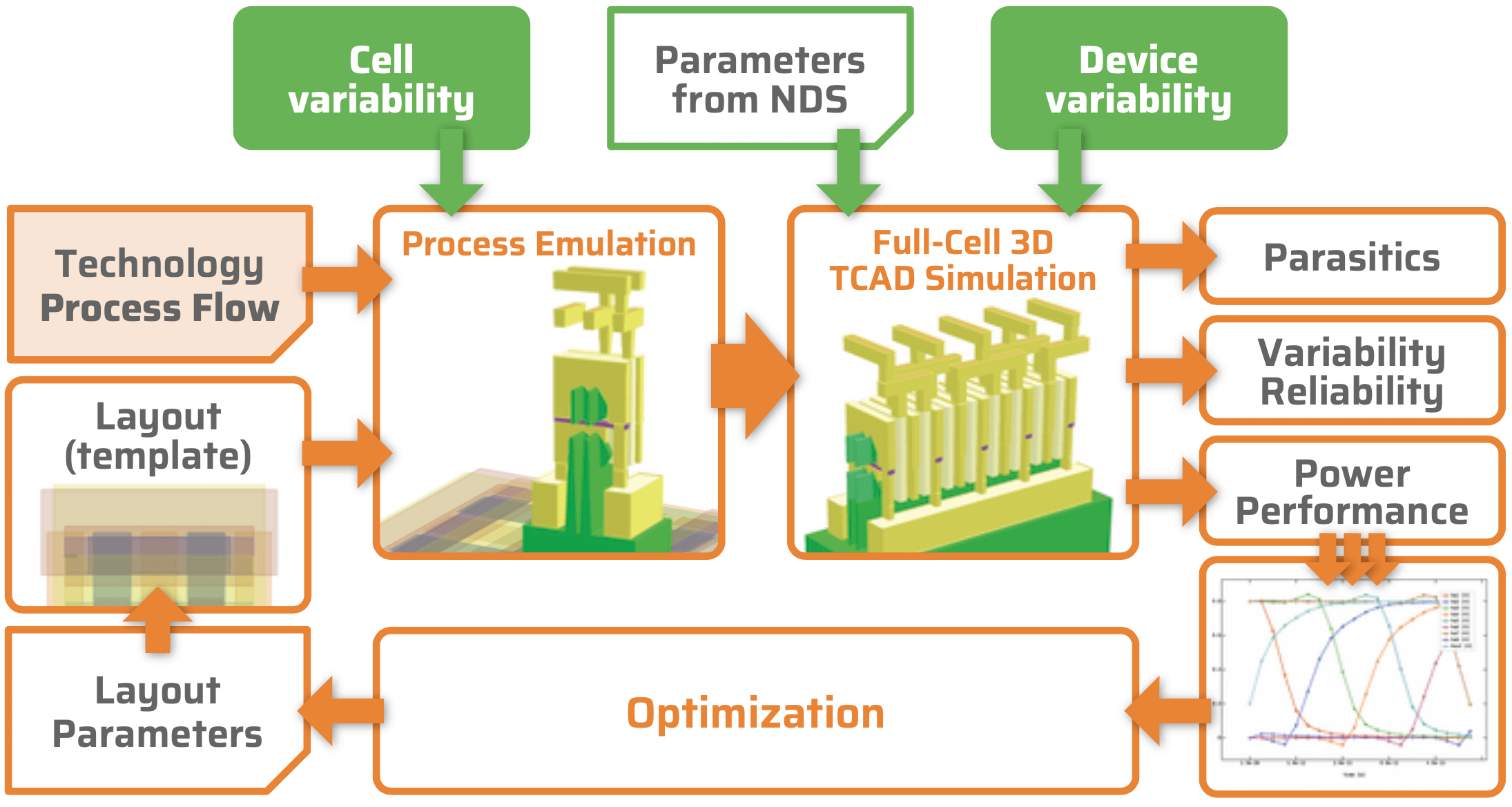

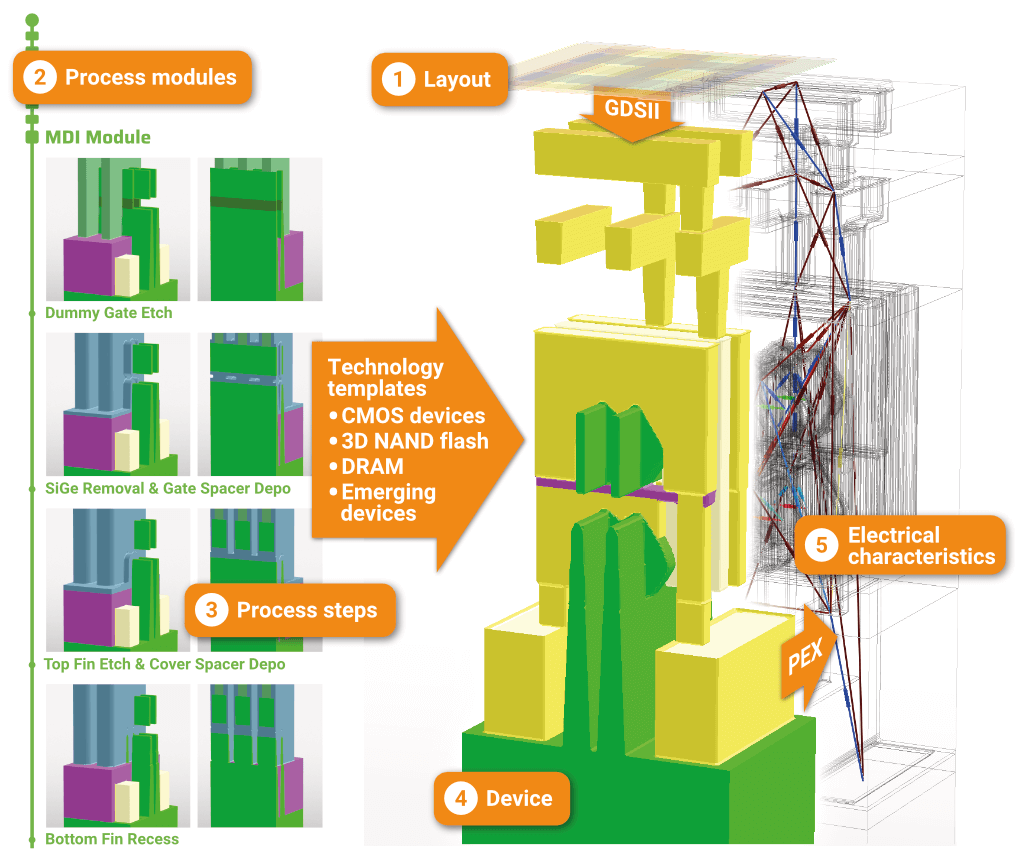

Process flow design, variability & yield, DTCO – GTS is presenting a solid DTCO flow with the process included: Use flexible process modules to easily explore designs for new technology platforms. Study variability and optimize for device PPA as well as production yield.

DTCO with the Process in Mind

Use your mask layouts and customize easy-to-use technology process flows to investigate single devices, cells, and circuits. Add process variation in your flow and understand critical process steps and their impact on power, performance, variability, and reliability. Optimize your process to get the most out of your FinFET, NSFET, NWFET, CFET designs!

Process-Aware DTCO with GTS ProEmu

GTS ProEmu conveniently brings the process to DTCO – a perfect match with GTS CellDesigner. Use predictive device simulations (with GTS Nano Device Simulator NDS), TCAD, 3D RC-extraction, and Spice simulations in unison, to optimize your process, design, and technology – All integrated in GTS Framework, which provides an efficient and comprehensive workplace with built-in optimization.

- Study variability in masks and processes

- Identify critical process steps

- Examine effects down the line

- Assess the impact on reliability

Understand how each process step affects device performance. Explore key technology parameters with design and process in mind.

Meet us at DAC 2023, Booth 2420

Visit us at DAC 2023 – GTS CEO Markus Karner and GTS Scientist Dr. Xaver Klemenschits will be happy to discuss how GTS tools can assist you in efficiently designing the best process flow for your next-generation FET!

60. Design Automation Conference (DAC) 2023

July 9-13, Moscone West, San Francisco

- Visit the DAC web site

- Find us at booth 2420 – Locate the GTS booth on the DAC floorplan

Keywords: process emulation, topography simulation, parasitics extraction (PEX), netlist, RC-extraction, circuit simulation, variability-aware design, nanosheet, FinFET, CFET, PPA