Know Your Circuit, the Earlier the Better

Boosting Productivity

Setting up new simulations has often turned out to be quite tedious in conventional tools, involving editing configuration files and node lists. With its intuitive user interface and integrated work flow functions, GTS Cell Designer is the most efficent-to-use DTCO tool suite available today, allowing users to concentrate on the task rather than the tools. Starting from device layout, building up detailed 3D cells, it is straight-forward to evaluate the performance of your design.

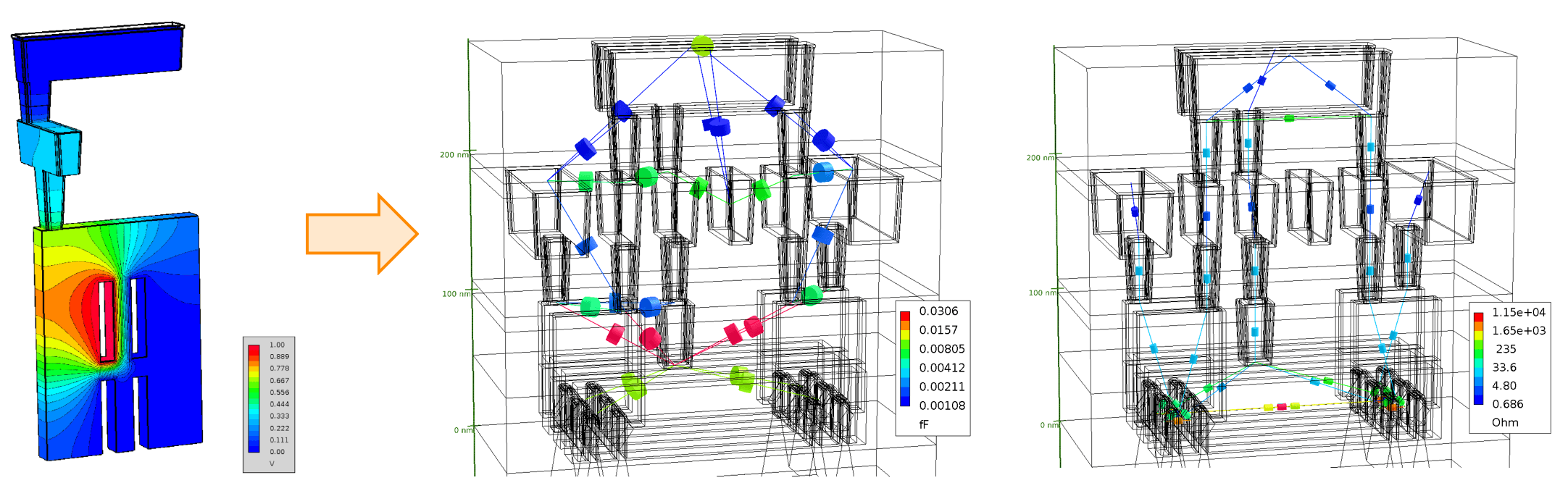

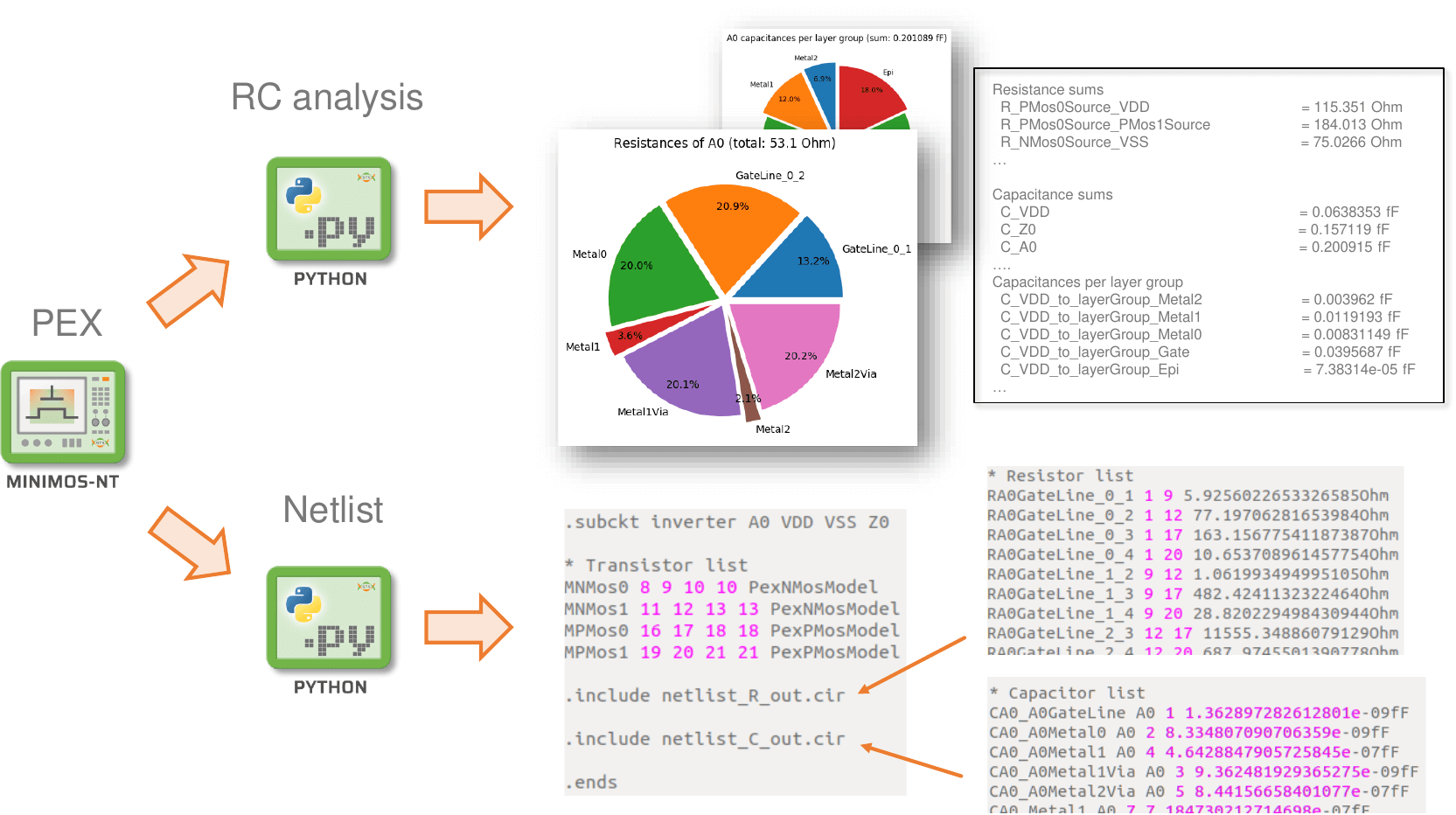

Parasitics Extraction (PEX)

Directly integrated in GTS’ device simulator Minimos-NT is a push-button solution to extract the resistances, capacitances, and transistor terminals of 2D and 3D TCAD structures. This Parasistics EXtraction (PEX) tool utilizes a highly efficient implementation of the Impedance Field Method (IFM) to apply perturbation potentials on top of converged quasi-stationary device simulations. The resistances and capacitances are then evaluated based on the perturbation responses and intelligent transistor detection completes the netlist. This parasitic extraction using a field-solver inherently includes the device simulation models, ensuring most accurate results.

In addition to the basic information about the netlist, and the resistance and capacitance values, the PEX results also include information about the segments, interfaces, materials, etc. of the analyzed TCAD structure. This allows for powerful post-processing to obtain for example total contact resistances (e.g. of the input terminal A0), all capacitances per layer (e.g. between A0 and Z0), netlists in arbitrary file formats (e.g. SPICE), and much more.

Netlists generated with the PEX tool are complete and ready-to-run except for the model descriptions of the transistors. These transistor models for accurate SPICE simulations can be obtained using the GTS Spice Model Extractor.

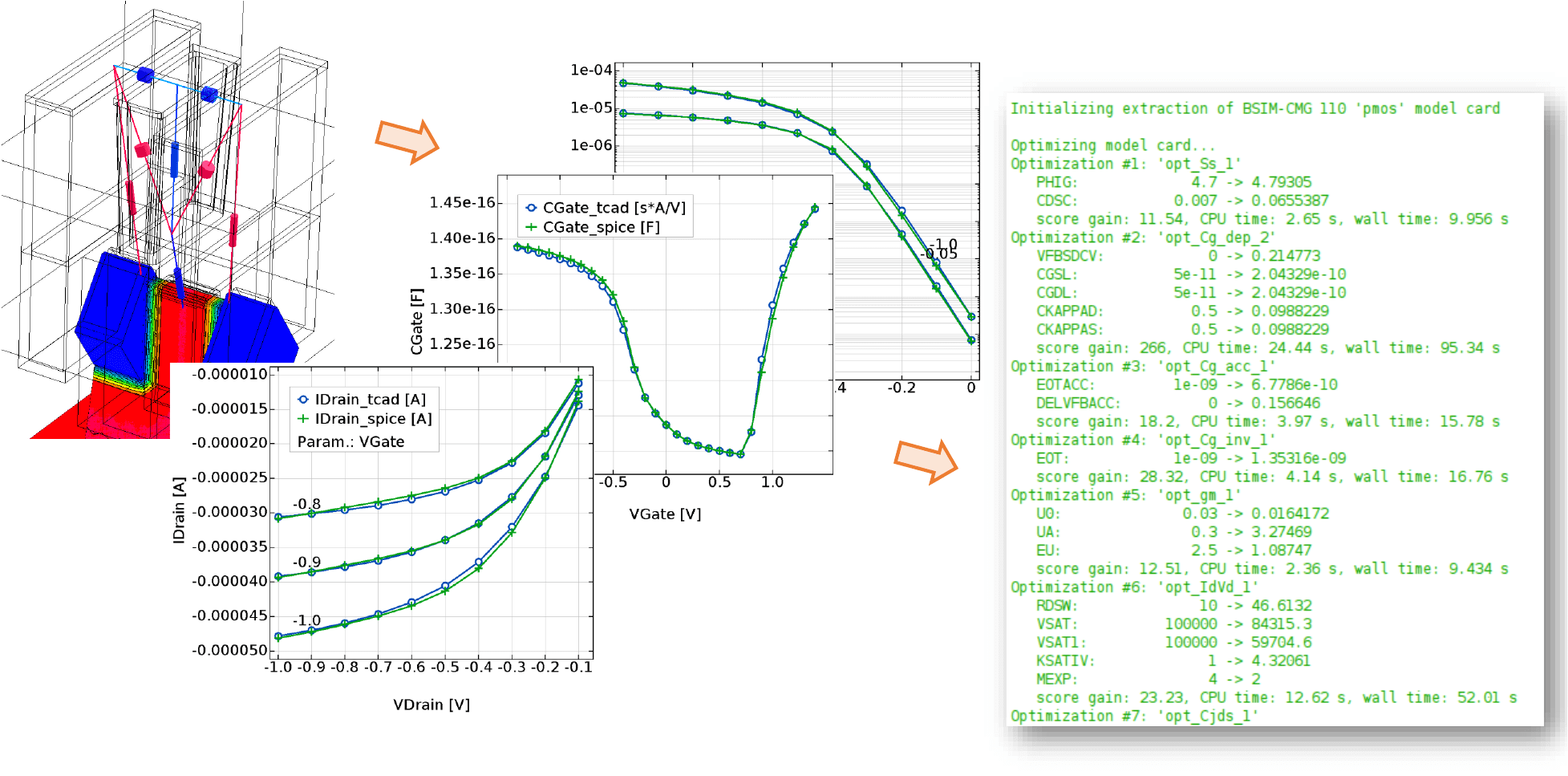

Spice Model Extractor

The PEX tool integrated in the device simulator allows for the most accurate SPICE model card parameter analysis: all parasitics and transistor characteristics are evaluated consistently and used in the GTS Spice Model Extractor to evaluate the model card parameters in a most meaningful way. This extraction is available for BSIM-CMG model cards as a push-button solution which can be fully customized through configuration inputs and, for even more flexibility, through Python code modification.

The netlist from GTS PEX combined with the transistor model card from the GTS Spice Model Extractor is all that’s needed for fast and accurate SPICE simulations using GTS Spice or any 3rd party SPICE solver. In summary, these push-button tools of the GTS Cell Designer offer a powerful alternative to pure TCAD solutions – while being much faster and versatile, yet very accurate.

GTS Cell Designer – implements a revolutionary sleek work flow for optimizing circuit designs for various technologies specifically, either without going into process details (LSG), or with the process included (ProEmu).