24. November 2021

Physical Device Simulation Boosting DTCO

Meet the GTS COO Oskar Baumgartner in real physical space, learn how physics-based device simulation boosts DTCO and path-finding as well as optimizing for reliability and yield. In fact, it is a prerequisite for getting dependable and accurate predictions for upcoming technology nodes.

Performance and Variability-Aware SRAM Design for GAA Nanosheets at 3nm

Discuss with us our extensive work on SRAM DTCO, investigating the details on power and performance under variability for nanosheets (horizontal nanosheets, NSH); Take a look how the NSH technology with its extended design space competes against FinFET at technologically relevant 3nm dimensions.

For the 3nm technology node, horizontal gate-all-around nanosheet devices offer a non-disruptive process transition from fin technologies, with the advantage of full 3D design flexibility and better short-channel control. For SRAM cell design, this enables non-digital n/pFET balancing.

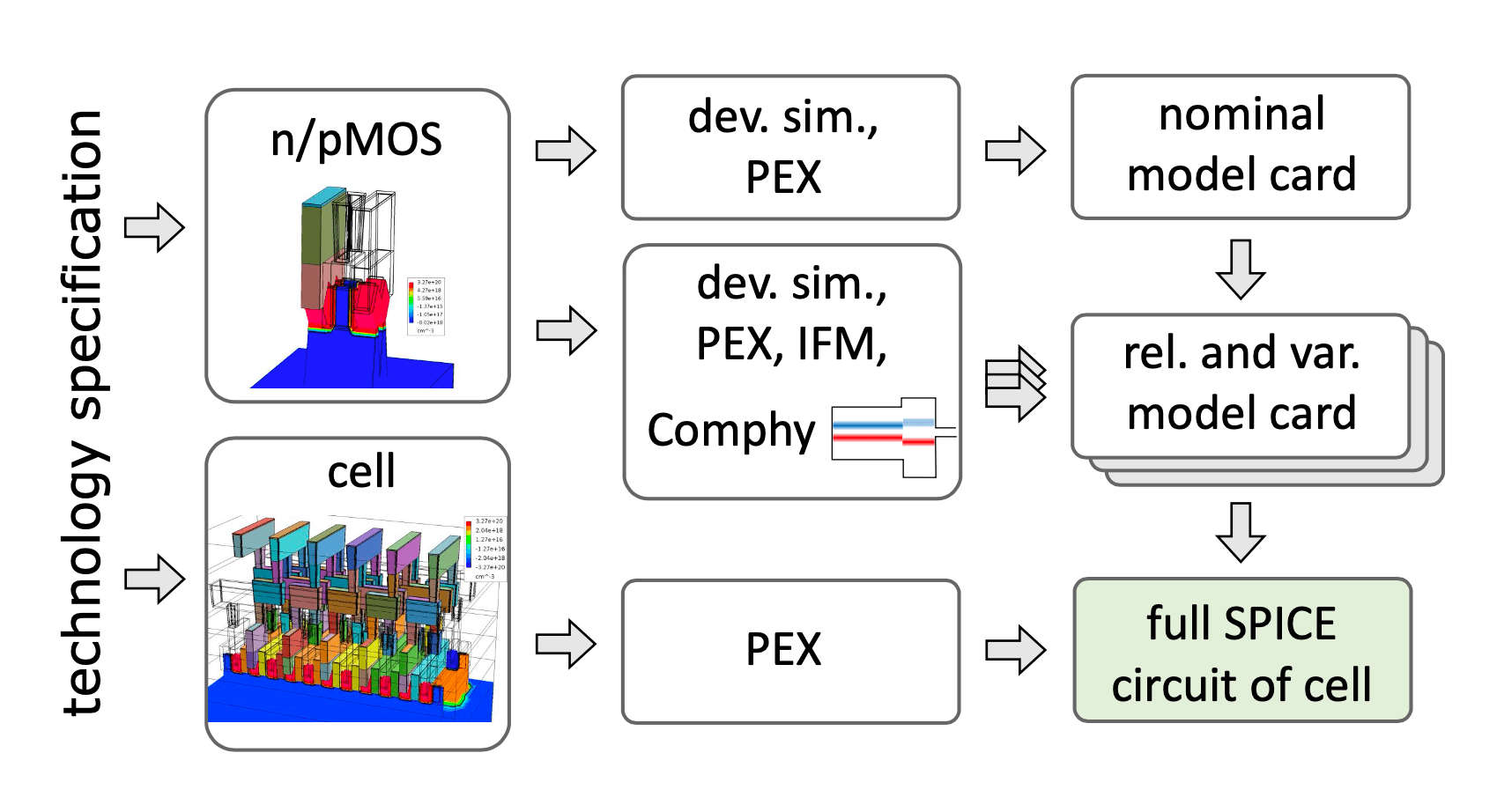

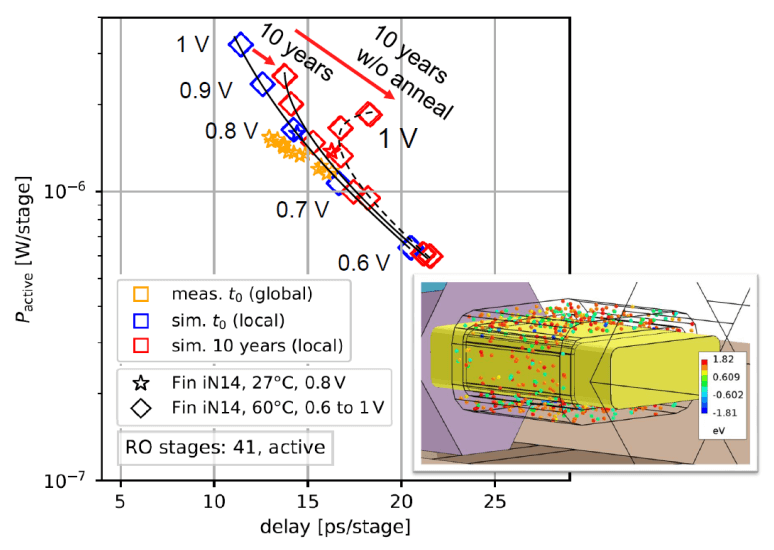

Reliability and Variability-Aware DTCO Flow / N3 FinFET and Nanosheet

In his IRPS presentation, our senior scientist Gerhard Rzepa demonstrated a reliability and variability-aware DTCO flow with logic cells. This is essential to correctly analyze and predict performance of upcoming technologies. Gerhard’s simulation flow for DTCO combines the accuracy of TCAD with the performance of SPICE – utilizing parasitic extractions (PEX), the impedance field method for variations, and the compact-physics simulator Comphy for reliability.

Needless to say, Gerhard found good agreement with experimental RO performance of iN14. Based on this, he made projections to N3 FinFET and nanosheet technologies.

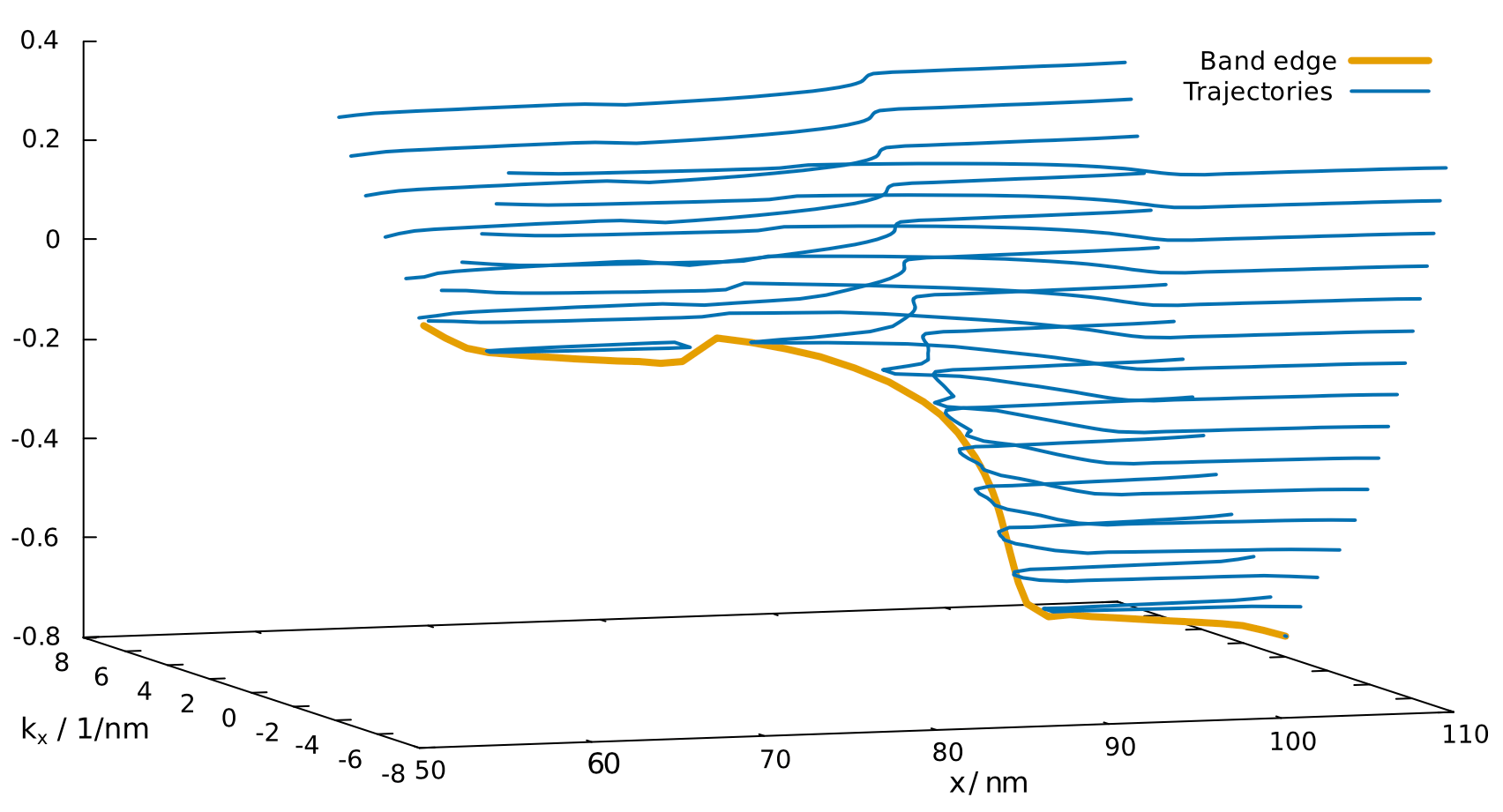

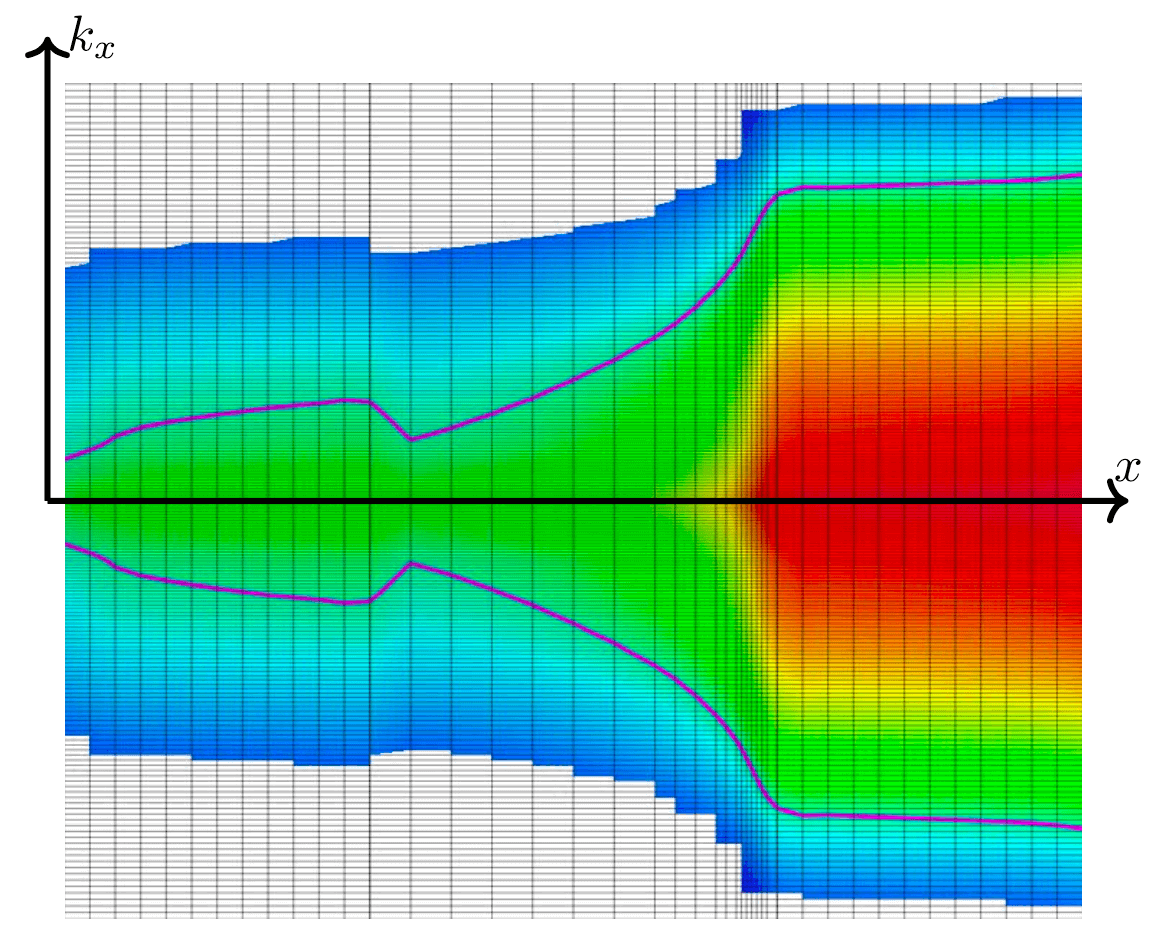

Relying on an Apt Tool: A Practical Subband-BTE Solver for Path-Finding and DTCO

Things can turn out easier than expected – when using the right tool.

In his recent TED paper, GTS CTO Zlatan Stanojević presents an in-depth discussion on the subband Boltzmann Transport (SBTE) methodology. He shows a wide range of applications that SBTE is perfect for, including state-of-the art non-planar and well-established planar technologies. Zlatan demonstrates how SBTE can be employed both as a path-finding tool and as a fundamental component in a DTCO flow.

DAC – Design Automation Conference 2021

Visit us at booth 2463 (near poster sessions) at DAC 2021 | December 5-9 | San Francisco

Referenced Papers:

- IRPS 2021 / G. Rzepa: News article • Paper

- TED 2021 / Z. Stanojević: News article • Paper

- SISPAD 2021 / M. Karner: News article • Paper