7. September 2023

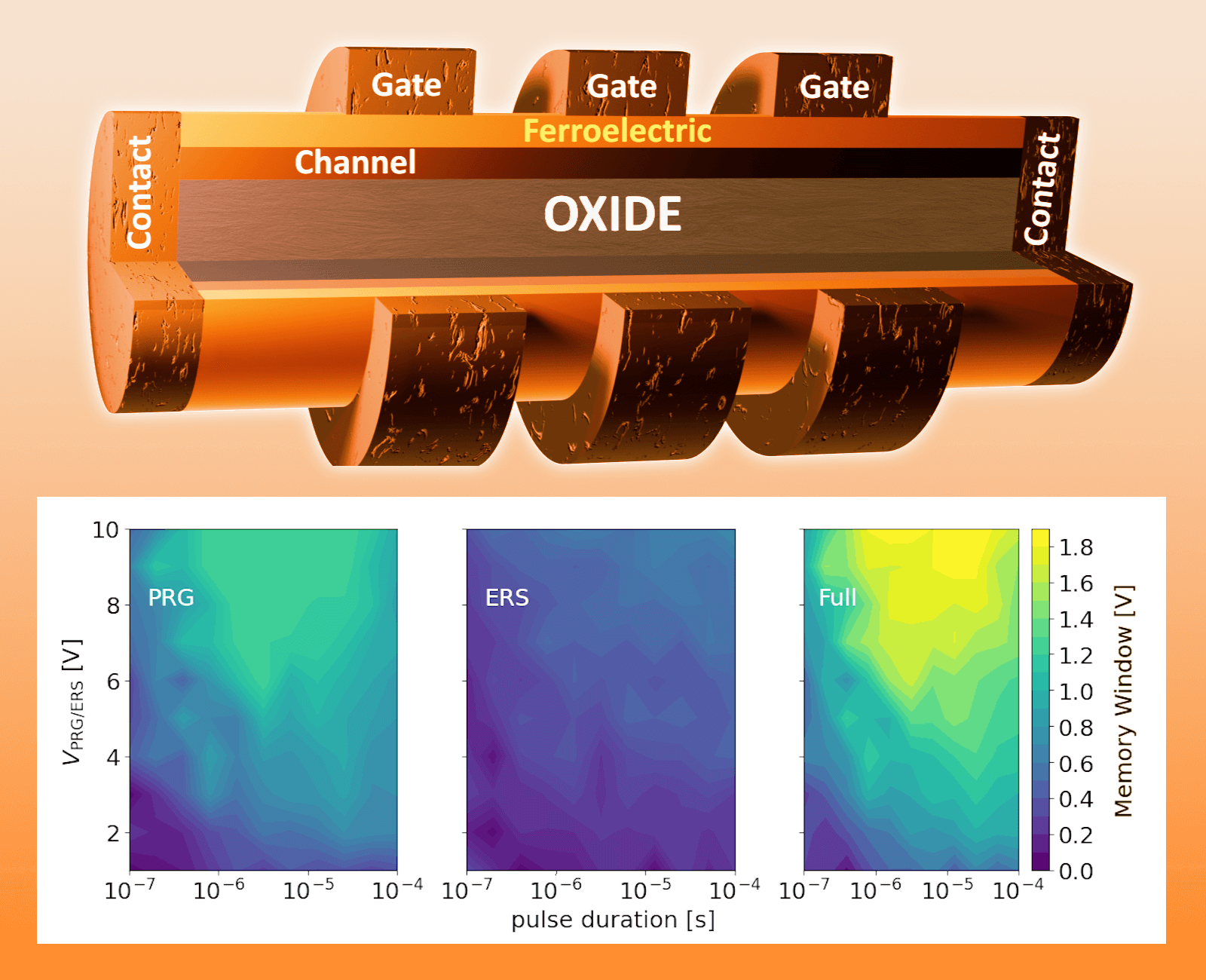

Simulation of 3D Ferroelectric Vertical NAND Memories

Visit booth 03 in Lisbon, where GTS Senior Scientist Mischa Thesberg will show how GTS Framework can be used to simulate a complete Ferroelectric Vertical NAND (Ferro-VNAND) memory device.

Come see how the competing effects of ferroelectricity and charge trapping can be combined in a single simulation to produce an investigation work-flow that nicely matches experiment results from literature.

Have a chat with GTS CTO Zlatan Stanojević, and discuss what GTS tools and services can do for you!

ESSCIRC/ESSDERC 2023 in Lisbon

September 11-14, 2023; GTS welcomes you at booth 03 in the exhibits area.

ESSDERC/ESSCIRC web site: esscirc-essderc2023.org

Keywords: VNAND, ferroelectric