GTS @IEDM2023 – Process to Circuit

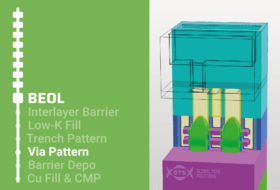

DTCO Flows that Work: Process – physics-based device simulation – circuit simulation. All covered in GTS Framework.

To narrow your search, add more words.

Example queries: dtco / subband boltzmann / finfet tutorial / vnand example / degradation publication ieee

DTCO Flows that Work: Process – physics-based device simulation – circuit simulation. All covered in GTS Framework.

In a performance & variability-aware DTCO flow, we benchmark Gate-all-around nanosheets for 3nm. Despite lower parasitic capacitances of fins, nanosheet SRAMs achieve better Vmin, read delay, and footprint.

DTCO Flows that Work: Why physics-based device simulation in fact is a prerequisite for getting dependable and accurate predictions for upcoming technology nodes.

GTS Scientist Franz Schanovsky will be co-chairing the session Emerging Transistor Reliability and Pertinent Strategies

Visit the GTS booth in the IEDM exhibits area and join our presentation at MOS-AK workshop on Dec 5!

Visit the GTS booth in the IEDM exhibits area to learn about our latest products and developments!

We present a physical modeling approach that explains the non-ideal ISPP slope in charge trap layer (CTL) flash memory and its impact on 3-D NAND vertical pitch scaling. First, we derive an expression for the VT change rate and use its field dependence to reproduce experimental vertical NAND ISPP slopes. Next, we implement a 2.5-D TCAD model based on these insights and show significant program voltage increase (>5V) in realistic 3-D NAND flash devices with scaling vertical pitch (down to 10nm). Finally, we evaluate high-k CTL and airgaps as mitigation measures at scaled pitch.

1 MB

For the 3nm technology node, horizontal gate-all- around nanosheet devices offer a non-disruptive process tran- sition from fin technologies with the advantage of full 3D design flexibility and better short-channel control. For SRAM cell design, this enables non-digital n/pFET balancing. In this paper, a performance and variability-aware DTCO flow is used to benchmark nanosheet SRAM cells against fin technologies at 3nm node, targeted at 45 nm CPP and 21 nm MP. The impact of gate length, fin height, number of nanosheets, effective n/pFET widths, channel doping, and vertical nanosheet pitch is studied. Despite the lower parasitic capacitances of fins, the design freedoms of nanosheets enable superior SRAM operation in terms of both Vmin and read delay even at smaller cell areas.

2 MB

Using an advanced simulation framework we analyze a recent sub-10 nm technology demonstration based on stacked nanowire transistors (NW-FETs). The study encompasses (i) topography simulation which realistically reproduces the fabricated device, (ii) device simulation based on the subband Boltzmann transport equation (iii) a comprehensive set of scattering models for the gate stack, (iv) physical models for time-zero variability and BTI device degradation. We find that (i) the fabrication process introduces parasitic capacitances not present in a comparable FinFET, (ii) the device performance is significantly affected by interface-charge-induced Coulomb scattering resulting in up to 50% reduction in drain current compared to an ideal device, (iii) device time-zero variability is increased due to a lower amount of dopant atoms per device, (iv) the device is more affected by BTI than a comparable FinFET. Using physics-based TCAD for technology path-finding and device optimization, we are able to point out critical improvements required for the stacked NW-FET to surpass current FinFET technology.

2 MB

We conduct a comprehensive simulation study of non-planar n-type channels based on consistent, physical models containing measurable quantities rather than fit-parameters. This contrasts empirical thin-body models used in classical/quantum-corrected TCAD. The method involves the self-consistent solution of the two-dimensional Schrödinger-Poisson system,rncombined with linearized Boltzmann transport in the third dimension. We advance the art of simulation by (i) introducing quantum simulation on unstructured meshes for arbitraryrngeometries, (ii) providing an efficient framework for rapid evaluation of device designs, and (iii) contributing a surface roughness scattering model for arbitrarily shaped surfaces.rnConsistent modeling allows us to make reliable assertions with respect to device performance.

1 MB

We go far beyond classical TCAD in and create a simulation framework that is ready for devices based on contemporary and future technology nodes. We do so by extending the common drift-diffusion-type device simulation framework with additional tools: (i) a k p-based subband structure tool, (ii) a deterministic subband Boltzmann transport solver, and (iii) a TCAD-compatible quantum transport solver, to capture every important aspect of device operation at the nano-scale. An atomistic ab-initio tool suite complements the framework providing material properties that would be hard to obtain otherwise. The capabilities of the approach are demonstrated on two different devices featuring non-planar geometry and alternative channel materials.

2 MB

We have completely revised our web site, for more clarity, improved experience on mobile devices, and a better MyGTS.